# Rethinking Computer Architecture

Wen-mei Hwu

University of Illinois, Urbana-Champaign

Celebrating Yale@75 September 19, 2014

# What Yale and I debate about in Samos and other places.

| Problem                    |                                       |

|----------------------------|---------------------------------------|

| Algorithm                  |                                       |

| Program                    | Application developers                |

| ISA (Instruction Set Arch) | should not deal with variations in HW |

| Microarchitecture          |                                       |

| Circuits                   |                                       |

| Electrons                  |                                       |

Patt and Patel, Introduction to Computer Systems: from Bits and Gates to C and Beyond

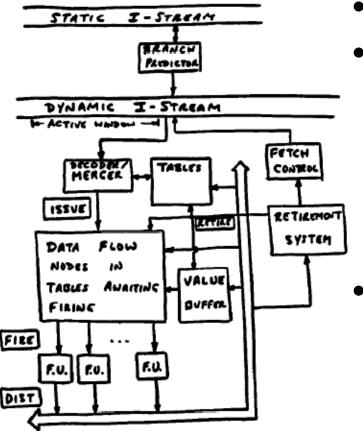

### The HPS Vision - 1985

ce of ıodel. flow : the tier t ighly ıctive f the very eeded flow

uting First, e few th to essing there ıch as nents,

ith its above odel is their ine at nd I/O stalls. n fire. " The Since ıg due

des to The

FIGURE 1.

One static program (algorithm)

Many execution resource configurations

- Types of Function Units

- Number of Function Units

- I-Fetch bandwidth

- Memory Latencies

#### Key enablers

- Branch prediction

- Resource mapping

- Restricted data flow execution

- Sequential retirement

at one time. We define the active window as the set

data flow graph for the entire program is in the machi Patt, Hwu, Shebanow, "HPS, A New ISP instructions whose corresponding data flow nodes: Microarchitecture: Rationale and Initial Results

### Some Lessons Learned

- Parallelism and communication costs motivate algorithm changes

- Locality vs. parallelism tradeoffs in libraries

- Performance and efficiency pressure breaks abstraction

- Java is great for abstraction portability but insufficient for performance and efficiency

- MPI, OpenMP apps often explicitly handle hardware-centric details

## Productivity and Performance

#### **Triolet**

```

ys = [sum(x * cos(r*k) for (x, k) in zip(xs, ks))

for r in par(rs)]

```

Library functions factor out data decomposition, parallelism, and communication

| 128-way Speedup<br>(16 cores × 8 nodes) | Triolet | C with MPI+OpenMP |

|-----------------------------------------|---------|-------------------|

|                                         | 99      | 115               |

#### C with MPI+OpenMP

```

!"#$!%&"'#&()*+,!%&"'"-.

!/01'2)%%'+"345/01'26//'7689:,!;%&"'#&()*+<.

|/01'2)%%'(=#>5/01'26//'7689:,!;%&"'"-<.

|*)#+$!"#$!(=#>?!@!%&"'"-!@@!?.

!/01'A*=+$5;+"34'B,!C,!/01'1DE,!?,!/01'26//'7689:<.

!/01'A*=+$5;+"34'>,!C,!/01'1DE,!?,!/01'26//'7689:<.

!*\#±$!"#$!*FG#5'±"34'R!@!*4"H="T5±"34'R.|%&"'#&()*±<.

*)#+$!"#$!&=--4-'+"34'B!@!*FG#>'+"34'B!J!%&"'#&()*+.

!!!>+!@!"#&G$'>+.

!!!B+!@!"#&G$'B+.

!4H+4!L

!!!>+!@!%=HH)*5+"34'>!J!+"34)K5KH)=$<<.

!!!B+!@!%=HH)*5+"34'>!J!+"34)K5KH)=$<<.

!KH)=$!J(+'*FG#>!@!%=HH)*5*FG#>'+"34'B!J!+"34)K5KH)=$<<.

!KH)=$!JN+'*FG#>!@!%=HH)*5*FG#>'+"34'B!J!+"34)K5KH)=$<<.

!!"#$!#0)(>4(+!@!%&"'#&()*+PC.

!!/01'84QG4+$!J(4Q+!@!%=HH)*5WO)(>4(+!J!R!J!+"34)K5/01'84QG4+$<<.

!!K)(!50!@!?.!0!5!#0)(>4(+.!0TT<!L

!!!"#$!0)(>4('"-!@!OTC.

!!!!!/01'1+4#-5>+,!+"34'>,!/01'U96VE,!0)(>4('"-,

!!!!!!!!!!!?,|/01'26//'7689:,|;(4Q+W#O)(>44+TOX<.

!!!!/01'1+4#-5(+!T!O)(>4("-J"FGW>'+"34'B,!*FGW>'+"34'B,!/01'U96VE,!O)(>4('"-,

!!!!!!!!!!!!?,!/01'26//'7689:,!;(4Q+WYJ#0)(>4(+TOX<.

!!%4%*&N5(+'*FG#>,!(+,!*FG#>'+"34'B!J!+"34)K5KH)=$<<.

!!!/01'7="$=HH5#0)(>4(+JR,!(4Q+,!/01'ZEVE[Z\Z'1]D68\<.

!!!K(445(4Q+<.

!!!/01'84*15>+,!+"34'>,!/01'U96VE,!?,

!!!!!!!!!!!!!?,!/01'26//'7689:,!/01'ZEVE[Z'1]D68\<.

!!!/01'84*I58+,!+"34'>,!/01'U96VE,!?,

!!!!!!!!!!!!?,!/01'26//'7689:,!/01'ZEVE[Z'1]D68\<.

!!!/01'84*I5(+'*FG#>,!*FG#>'+"34'B,!/01'U96VE,!?,

!!!!!!!!!!!!!?,!/01'26//'7689:,!/01'ZEVE[Z'1]D68\<.

```

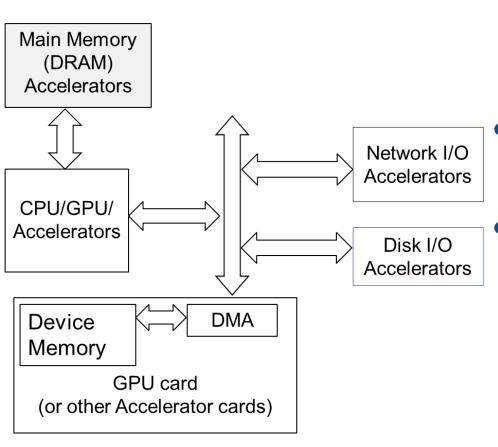

## Trends in System Design – 2014

- CPUs/GPUs/Accelerators or entire nodes are the new function units

- Compute functions are the new instructions

- Distributed execution of functions to avoid data movement

- Accelerators in/near

Network I/O, Disk I/O,

DRAM

- Some come with own

DRAM/SRAM for bandwidth

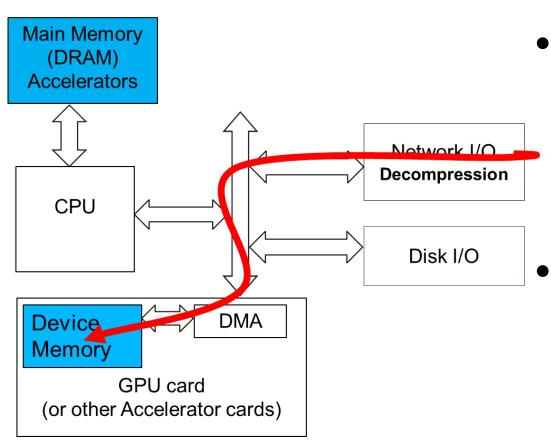

# **Example - Desirable Data Transfer and Compute Behavior**

- Runtime/OS should map buffers and compute functions

- I/O buffer to any major DRAM/SRAM

- Compute functions (decompression) to any CPU/GPU/accelerators

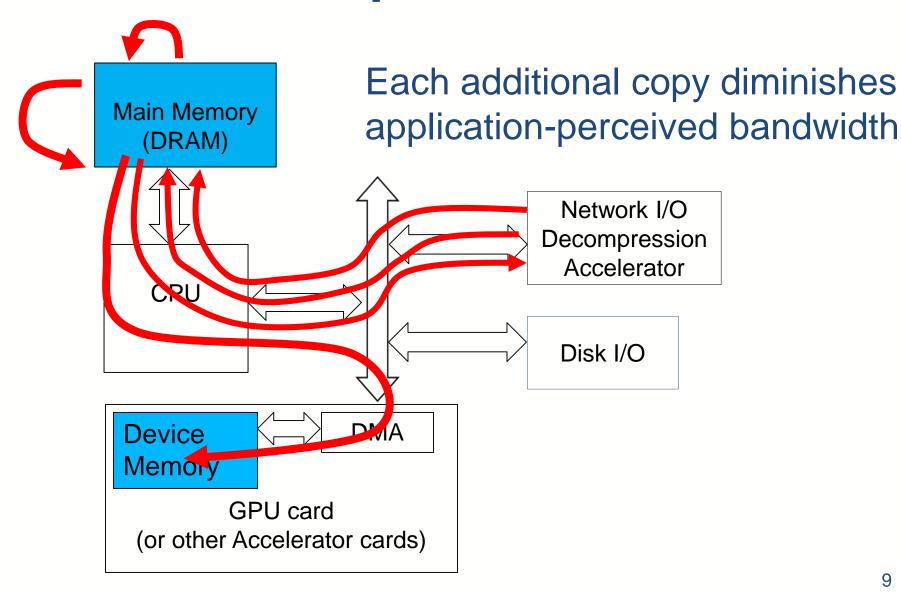

## **Example -Today's Data Transfer** and Compute Behavior

### A Call to Action

- Redefine system architecture

- HAS/CUDA 6.0 a step in the right direction

- Redefine ISA binary standard

- SPIR/HSAIL/PTX with finalizers a step in the right direction

- Redesign OS/Runtime for data and compute mapping

- UNIX/Linux overdue for redesign

- Provide performance portable domain libraries to sustain abstraction

- High-level mechanisms such as Triolet and Tangram to fuse and tune library code into apps

## Congratulations, Yale!